## DEVELOPMENT AND BENCHMARKING OF NEW HARDWARE ARCHITECTURES FOR EMERGING CRYPTOGRAPHIC TRANSFORMATIONS

by

Marcin Rogawski

A Dissertation

Submitted to the

Graduate Faculty

of

George Mason University

In Partial fulfillment of

The Requirements for the Degree

of

Doctor of Philosophy

Electrical and Computer Engineering

| Committee: |                                                           |

|------------|-----------------------------------------------------------|

|            | Dr. Kris Gaj, Dissertation Director                       |

|            | Dr. Jens-Peter Kaps, Committee Member                     |

|            | Dr. Qiliang Li, Committee Member                          |

|            | Dr. Massimiliano Albanese, Committee Membe                |

|            | Dr. Andre Manitius, Department Chair                      |

|            | Dr. Kenneth S. Ball, Dean, Volgenau School of Engineering |

| Date:      | Summer Semester 2013 George Mason University Fairfax, VA  |

Development and Benchmarking of New Hardware Architectures for Emerging Cryptographic Transformations

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Marcin Rogawski Master of Science Military University of Technology, 2003

Director: Dr. Kris Gaj, Associate Professor Department of Electrical and Computer Engineering

> Summer Semester 2013 George Mason University Fairfax, VA

Copyright  $\bigodot$  2013 by Marcin Rogawski All Rights Reserved

#### Dedication

I dedicate this dissertation to my beloved wife and constant advocate, Kasia. Her patience, trust and support during these years in withstanding all the hours lost to my studies was critical to my success. To my mother Danusia and my stepfather Bohdan, who gave me the character and goal-oriented attitude, which has enabled me to get this far. To my parents-in-law Jadwiga and Czesław, who always believe, that my crazy ideas will work. Finally, I dedicate this thesis to the memory of my father Stanisław.

#### Acknowledgments

This research was partially supported by National Institute of Standards and Technology through the Recovery Act Measurement Science and Engineering Research Grant Program, under contract no. 60NANB10D004 (*Project title: Environment for Fair and Comprehensive Performance Evaluation of Cryptographic Hardware and Software*).

It is my great pleasure, but also a must, to acknowledge multiple individuals who supported me directly or indirectly in closing successfully this important chapter of my life.

First of all, I want to thank my advisor, Prof. Kris Gaj. I owe a lot to him for his precious guidance, support, encouragement, and always friendly atmosphere. His open mind, broad spectrum of knowledge, and accurate thinking helped me accomplish my goals. He has been a great mentor as well as a source of inspiration throughout my PhD study.

Furthermore, I like to thank Prof. Jens-Peter Kaps for his very valuable time, remarks, and comments. All of them were always delivered in a very constructive, but also cheerful form.

I also thank other dissertation committee members, Prof. Qiliang Li and Prof. Massimiliano Albanese. They provided sustained guidance, comments, advice and made my defense in almost relaxed atmosphere.

I would like to thank Prof. Andre Manitius for everything he has done for me an my wife. He made my GMU study time almost stress-free!

The role of supportive and welcoming friends and colleagues in the life of a researcher can not be forgotten. I would like to thank all the present and former members of Cryptographic Engineering Research Group, with a special distinction for Ekawat Homsirikamol for our model cooperation.

Finally, I would like to thank my wife, my parents, my brothers, and my big family for their unconditional support and for taking care of me more than I sometimes deserved.

### Table of Contents

|     |        |         | 1                                                                      | Page |

|-----|--------|---------|------------------------------------------------------------------------|------|

| Lis | t of T | Tables  |                                                                        | vii  |

| Lis | t of F | igures  |                                                                        | X    |

| Ab  | strac  | t       |                                                                        | xi   |

| 1   | Intr   | oductio | on                                                                     | (    |

|     | 1.1    | Motiv   | ation                                                                  | (    |

|     | 1.2    | Summ    | nary of research contributions                                         | 7    |

|     |        | 1.2.1   | Novel hardware accelerator for authenticated encryption                | 7    |

|     |        | 1.2.2   | An adaptation of the T-box method to the AES-like hash functions       | 8    |

|     |        | 1.2.3   | A novel, adder/subtractor for thousand bit and more using fast carry   |      |

|     |        |         | chains of modern FPGAs                                                 | Ś    |

|     |        | 1.2.4   | New approach to arithmetic based on the Solinas primes for Pairing-    |      |

|     |        |         | based Cryptography                                                     | 6    |

|     |        | 1.2.5   | Novel hardware architectures for pairing on Edwards curves             | 10   |

|     |        | 1.2.6   | A heuristic strategy for FPGA-oriented electronic design automation    | 11   |

|     |        |         |                                                                        |      |

| Ι   | Hig    | gh-per  | formance hardware architectures supporting confidentiality             | y    |

| ar  | ıd in  | tegrit  | y                                                                      | 13   |

| 2   | Hig    | h-Thro  | ughput hardware architectures of AES-like Cryptographic hash functions | s 14 |

|     | 2.1    | Introd  | luction and motivation                                                 | 14   |

|     | 2.2    | Previo  | ous work                                                               | 17   |

|     |        | 2.2.1   | Grøstl in SHA-3 competition                                            | 17   |

|     |        | 2.2.2   | T-box method                                                           | 18   |

|     |        | 2.2.3   | Resource sharing                                                       | 20   |

|     | 2.3    | Table-  | -based method extension for AES-like cryptographic transformations     |      |

|     |        | (Grøst  | tl case)                                                               | 22   |

|     |        | 2.3.1   | T-box-based hardware architecture of Grøstl-0 and Grøstl               | 22   |

|     |        | 2.3.2   | Implementation results                                                 | 25   |

|     |        | 2.3.3   | Conclusions                                                            | 28   |

|    | 2.4  | Hardy                                                                             | vare architecture for the authenticated encryption based on Grøstl and |  |  |  |  |  |

|----|------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

|    |      | AES                                                                               |                                                                        |  |  |  |  |  |

|    |      | 2.4.1                                                                             | Authenticated encryption in IPSec                                      |  |  |  |  |  |

|    |      | 2.4.2                                                                             | Contribution                                                           |  |  |  |  |  |

|    |      | 2.4.3                                                                             | Authenticated encryption based on Grøstl and AES in a single copro-    |  |  |  |  |  |

|    |      |                                                                                   | cessor                                                                 |  |  |  |  |  |

|    |      | 2.4.4                                                                             | Coprocessor description                                                |  |  |  |  |  |

|    |      | 2.4.5                                                                             | Results                                                                |  |  |  |  |  |

|    |      | 2.4.6                                                                             | Conclusions                                                            |  |  |  |  |  |

| II | На   | ardwa                                                                             | re architectures for public key cryptography 49                        |  |  |  |  |  |

| 3  | FPO  | GA-orie                                                                           | ented adder for thousand bits and more 5                               |  |  |  |  |  |

|    | 3.1  |                                                                                   | luction                                                                |  |  |  |  |  |

|    | 3.2  | Previo                                                                            | ous work                                                               |  |  |  |  |  |

|    | 3.3  | The a                                                                             | dder                                                                   |  |  |  |  |  |

|    | 3.4  | Paran                                                                             | neters selection                                                       |  |  |  |  |  |

|    | 3.5  | Result                                                                            | ts discussion                                                          |  |  |  |  |  |

|    | 3.6  | Concl                                                                             | usion                                                                  |  |  |  |  |  |

| 4  | Hare | Hardware architectures for modular arithmetic based on the use of Solinas numbers |                                                                        |  |  |  |  |  |

|    | and  | heterog                                                                           | genous FPGA devices                                                    |  |  |  |  |  |

|    | 4.1  | Introd                                                                            | luction and motivations                                                |  |  |  |  |  |

|    | 4.2  | Previous work                                                                     |                                                                        |  |  |  |  |  |

|    | 4.3  | Archit                                                                            | sectures for the Solinas primes                                        |  |  |  |  |  |

|    |      | 4.3.1                                                                             | Modular adder/subtractor                                               |  |  |  |  |  |

|    |      | 4.3.2                                                                             | Mixed radix multi-operand addition                                     |  |  |  |  |  |

|    |      | 4.3.3                                                                             | Modular multiplier with Booth recoding and Barrett reduction 7         |  |  |  |  |  |

|    |      | 4.3.4                                                                             | Multiplication using DSP blocks                                        |  |  |  |  |  |

|    |      | 4.3.5                                                                             | Double-speed mode                                                      |  |  |  |  |  |

|    |      | 4.3.6                                                                             | Barrett reduction for Solinas primes:                                  |  |  |  |  |  |

|    | 4.4  |                                                                                   | usions                                                                 |  |  |  |  |  |

| 5  |      |                                                                                   | Edwards curves for speed-oriented applications                         |  |  |  |  |  |

| -  | 5.1  |                                                                                   | luction and motivation                                                 |  |  |  |  |  |

|    | 0.1  | 5.1.1                                                                             | Motivation                                                             |  |  |  |  |  |

|    |      | 5.1.2                                                                             | Contribution                                                           |  |  |  |  |  |

|    | 5.2  |                                                                                   | ous work                                                               |  |  |  |  |  |

|    | 5.3  |                                                                                   | pairing on twisted supersingular Edwards curves 9                      |  |  |  |  |  |

|    |      |                                                                                   | - · ·                                                                  |  |  |  |  |  |

|     |        | 5.3.1    | Twisted Edwards curves                                                    | 95  |

|-----|--------|----------|---------------------------------------------------------------------------|-----|

|     |        | 5.3.2    | Tate pairing on supersingular Edwards curves                              | 95  |

|     |        | 5.3.3    | Miller loop                                                               | 97  |

|     |        | 5.3.4    | Choice of parameters for supersingular curves with embedding degree       |     |

|     |        |          | k=2                                                                       | 101 |

|     |        | 5.3.5    | Final exponentiation                                                      | 102 |

|     | 5.4    | The co   | oprocessor                                                                | 106 |

|     | 5.5    | Hardw    | vare implementation results                                               | 118 |

|     |        | 5.5.1    | Note about software implementations                                       | 122 |

|     | 5.6    | Conclu   | usions                                                                    | 123 |

| II  | I E    | Benchn   | marking of FPGA-based coprocessors for cryptography                       | 124 |

| 6   |        |          | ting of hardware architectures for Cryptography                           | 125 |

| Ü   | 6.1    |          | Luction and motivation                                                    | 125 |

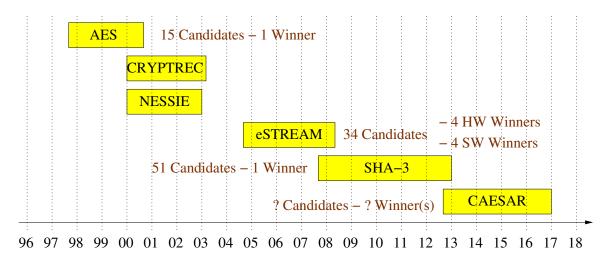

|     | 0.1    | 6.1.1    | Cryptographic Competitions                                                | 126 |

|     |        | 6.1.2    | Obstacles to a fair comparison                                            | 128 |

|     | 6.2    |          | ous work                                                                  | 129 |

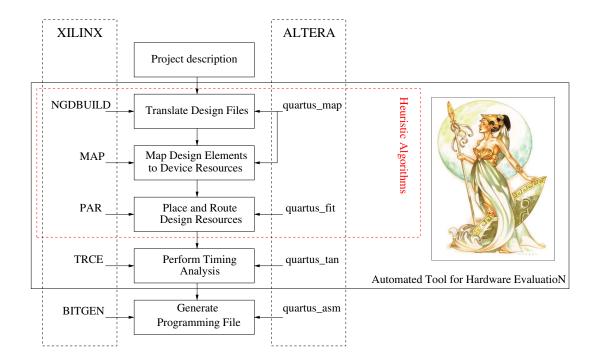

|     | 0.2    | 6.2.1    | Automated Tool for Hardware EvaluatioN                                    | 131 |

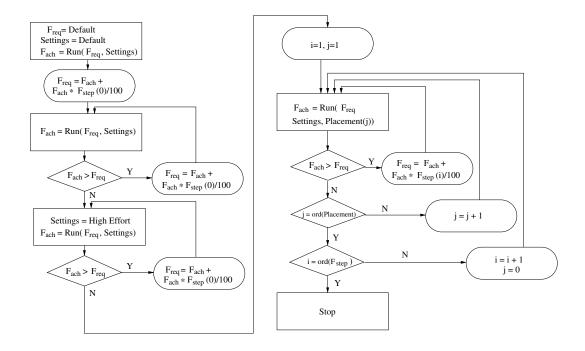

|     | 6.3    | A heu    | ristic optimization algorithm for FPGA-based hardware architectures       | 133 |

|     |        | 6.3.1    | A case study and the design rationale for the best ATHENa heuristic       |     |

|     |        |          | algorithm                                                                 | 133 |

|     |        | 6.3.2    | Heuristic optimization algorithms for FPGA design flow                    | 134 |

|     | 6.4    | Result   |                                                                           | 137 |

|     | 6.5    | Concl    | usions                                                                    | 139 |

| 7   | Cor    | nclusion | s and future research                                                     | 140 |

|     | 7.1    | Conclu   | usions                                                                    | 140 |

|     | 7.2    | Future   | e work                                                                    | 144 |

|     |        | 7.2.1    | Hardware architectures for pairing on ordinary Edwards curves $\ . \ .$ . | 144 |

|     |        | 7.2.2    | Hardware architectures for the Edwards Curves Digital Signature Al-       |     |

|     |        |          | gorithm based on P25519                                                   | 144 |

|     |        | 7.2.3    | Hardware architectures for the short digital signatures based on the      |     |

|     |        |          | Barreto-Naehrig curves                                                    | 145 |

|     |        | 7.2.4    | Hardware-Software co-design for Public Key Cryptography                   | 146 |

| Bil | oliogr | aphy.    |                                                                           | 148 |

### List of Tables

| $\Gamma$ al | ble  | P                                                                                                                                                     | age |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | 2.1  | Results of Implementations for High-Speed Architectures of Grøstl-256, using                                                                          |     |

|             | 2.2  | Xilinx Virtex 5 FPGAs                                                                                                                                 | 18  |

|             |      | geometry AxB is defined by A-bit address space and B-bit words                                                                                        | 20  |

|             | 2.3  | Hardware architectures supporting authenticated encryption at 128-bit security                                                                        | 21  |

|             | 2.4  | Timing characteristics and resource utilization for basic architectures and                                                                           |     |

|             |      | architectures based on the T-box method in case of four selected FPGA families. Notation: Tp - throughput, Mem-bits - number of memory bits, $\Delta$ |     |

|             |      | Tp - relative improvement in throughput, $\Delta$ Area - relative reduction in the                                                                    |     |

|             |      | number of basic reconfigurable resources, $\Delta$ Tp/Area - relative improvement                                                                     |     |

|             |      | in throughput/area                                                                                                                                    | 26  |

|             | 2.5  | IPSec Supported Protocols and Algorithms                                                                                                              | 29  |

|             | 2.6  | Number of rounds and the security level relations for Grøstl and AES $$                                                                               | 34  |

|             | 2.7  | Throughput-related parameters                                                                                                                         | 42  |

|             | 2.8  | Results of shared-resources implementation for HMAC-Grøstl-256 and AES- $$                                                                            |     |

|             | 2.9  | 128 in Counter Mode on modern FPGA                                                                                                                    | 44  |

|             | 2.10 | 256 in Counter Mode on modern FPGA                                                                                                                    | 44  |

|             |      | Altera Cyclone III                                                                                                                                    | 45  |

|             | 2.11 | Throughput/Area ratio relative improvement between this work and $[1]$                                                                                | 47  |

|             | 3.1  | Latency of the three major addition techniques as a function of the size of                                                                           |     |

|             |      | arguments                                                                                                                                             | 62  |

|             | 3.2  | Parameters exploration for the 1024-bit addition                                                                                                      | 63  |

|             | 3.3  | Parameters exploration for the 1024-bit modular addition                                                                                              | 64  |

| 3.4 | Implementation results for combinational versions of selected adders in the                              |     |

|-----|----------------------------------------------------------------------------------------------------------|-----|

|     | 1024-4096-bit range. $\Delta$ latency, $\Delta$ area, $\Delta$ latency $\cdot$ area - relative change in |     |

|     | comparison to the best of the two classical designs in terms of latency, area                            |     |

|     | and latency · area product, respectively.                                                                | 67  |

| 3.5 | Implementation results for the 1024-bit modular addition. $\Delta$ latency, $\Delta$                     |     |

|     | area, $\Delta$ latency $\cdot$ area - relative change in comparison to the either one of                 |     |

|     | two classical designs in terms of latency, area and latency $\cdot$ area product,                        |     |

|     | respectively                                                                                             | 68  |

| 4.1 | General Purpose Modular Multiplication/Inversion architectures for GF(p)                                 | 73  |

| 5.1 | Parameters of Solinas primes used for Tate pairing on supersingular twisted                              |     |

|     | Edwards curves                                                                                           | 100 |

| 5.4 | Scheduling of operations for Alg. 2, when $r_i = 1 \dots \dots \dots$                                    | 106 |

| 5.2 | Memory mapping and initialization                                                                        | 111 |

| 5.3 | Scheduling of operations for Alg. 2, when $r_i = 0$                                                      | 112 |

| 5.5 | Final exponentiation Alg. 7 scheduling.                                                                  |     |

|     | $\mathrm{MSP}(x)$ and $\mathrm{LSP}(x)$ - the most and the least significant parts of x-value,           |     |

|     | respectively.                                                                                            | 113 |

| 5.6 | Latency-related information for building transformations on different security                           |     |

|     | levels for Xilinx (Altera in parentheses)                                                                | 116 |

| 5.7 | Implementation results of the pairing coprocessors for selected FPGA devices                             | 119 |

| 5.8 | Pairing transformations speed records for the range of 120-128-bits security                             | 120 |

| 5.9 | Software implementations of pairing on (single core) Intel Core i<br>7 $2.8~\mathrm{GHz}$ .              | 121 |

| 6.1 | Benchmarking Tools for Cryptography                                                                      | 130 |

| 6.2 | Influence of design software options on implementation results for the opti-                             |     |

|     | mized architecture of SHA-256 by Chaves et al                                                            | 134 |

## List of Figures

| Figure |                                                                                                            | Page |

|--------|------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Digital signature generation and verification                                                              | 1    |

| 1.2    | Hierarchical model of Cryptographic applications. Major contribution of this                               |      |

|        | research marked with points 1-6                                                                            | 4    |

| 2.1    | Wide Trail Strategy family of cryptographic transformations was defined in                                 |      |

|        | [2]. Based on this strategy several algorithms have been invented: Shark [3],                              |      |

|        | Square [4], BaseKing [2], Rijndael-AES [5], Serpent [6], Twofish [7], Crypton                              |      |

|        | [8], Hiercorypt [9], Khazad [10], Anubis [11], GrandCru [12], Q [13], Noekeon                              |      |

|        | [14], ECHO [15], Fugue [16], Grøstl [17], SHAvite-3 [18] and JH [19]                                       | 19   |

| 2.2    | Phases in the Grøstl-0 round transformation to T-box representation                                        | 22   |

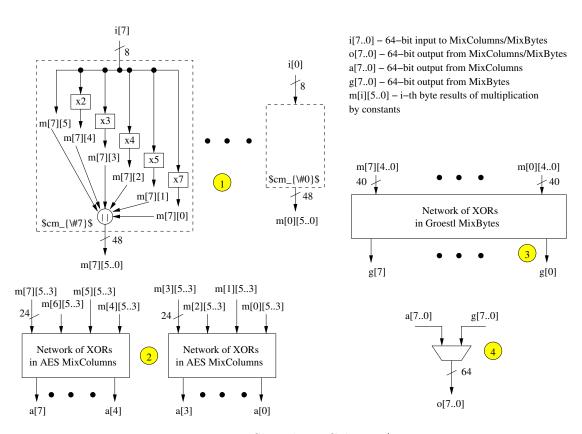

| 2.3    | The Grøstl's MixBytes operation                                                                            | 23   |

| 2.4    | The Grøstl's MixBytes operation based on reduced number of multipliers $$ .                                | 23   |

| 2.5    | Grøstl's MixBytes single input byte multiplication by five unique values $$                                | 23   |

| 2.6    | Grøstl's MixBytes table implemented as 256x40 bits ROM                                                     | 24   |

| 2.7    | Grøstl's round table implemented as 256x40 bits ROM                                                        | 24   |

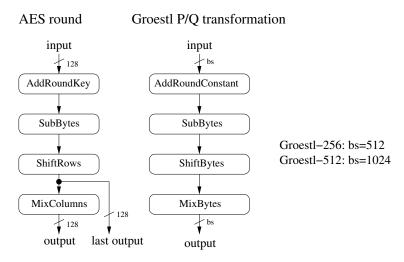

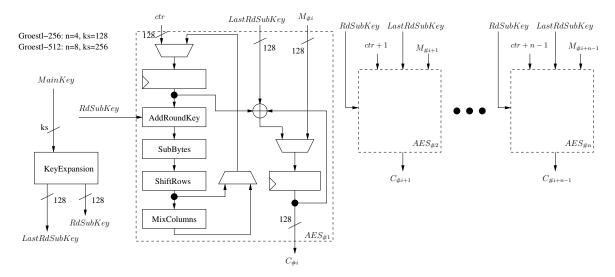

| 2.8    | Block diagram of Grøsl and AES round                                                                       | 30   |

| 2.9    | Shared MixColumns/Bytes                                                                                    | 32   |

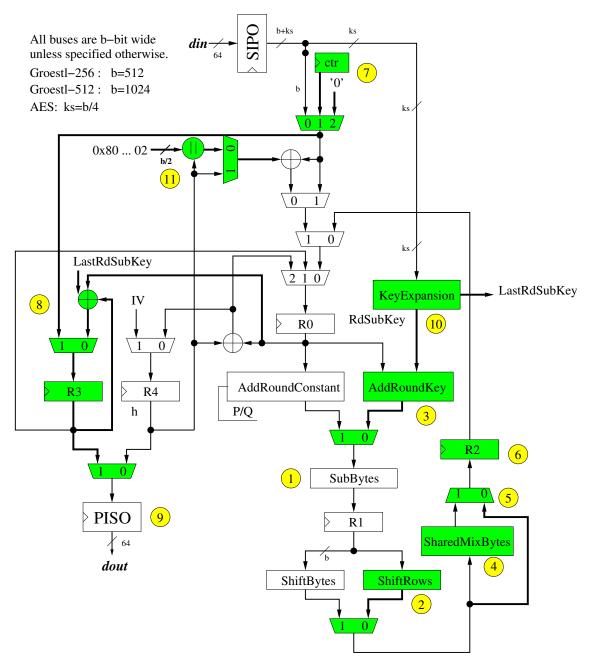

| 2.10   | Block diagram of Grøstl/AES core                                                                           | 33   |

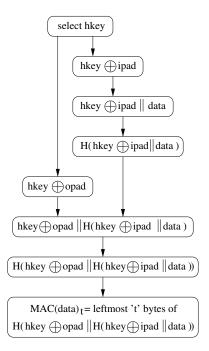

| 2.11   | HMAC generation                                                                                            | 36   |

| 2.12   | Block diagram of AES-CTR where $n$ is the number of AES cores                                              | 37   |

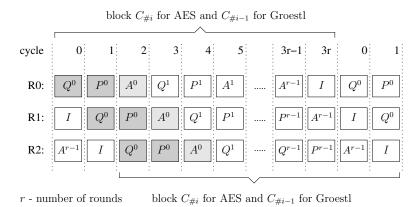

| 2.13   | Pipelining in the Computational Unit of the Grøstl/AES core                                                | 39   |

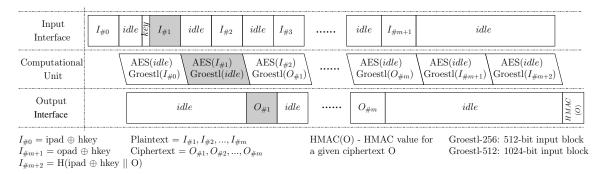

| 2.14   | High level scheduling in the Grøstl/AES core during encryption process $$                                  | 40   |

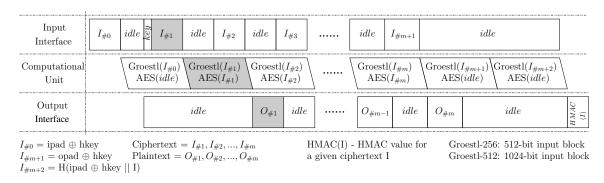

| 2.15   | High level scheduling in the Grøstl/AES core during decryption process $$                                  | 40   |

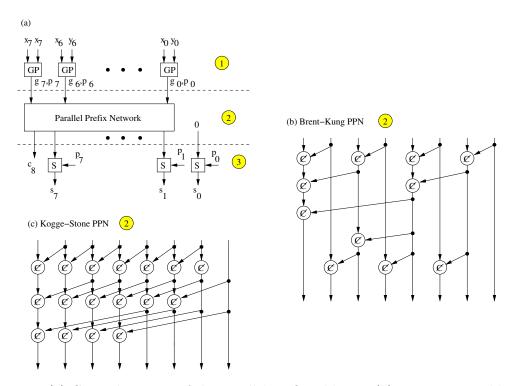

| 3.1    | (a) General concept of the parallel prefix addition, (b) Brent-Kung adder,                                 |      |

|        | (c) Kogge-Stone adder. GP: $g_i = x_i \cdot y_i, p_i = x_i \oplus y_i, S: s_i = p_i \oplus c_i, \not\in$ : |      |

|        | $g = g'' + g' \cdot p'', p = p' \cdot p''  \dots  \dots  \dots  \dots  \dots  \dots  \dots$                | 53   |

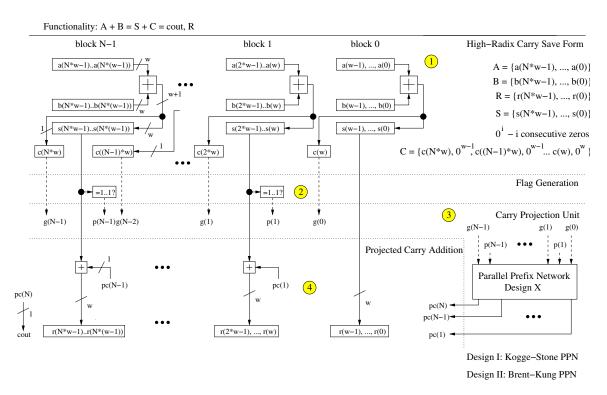

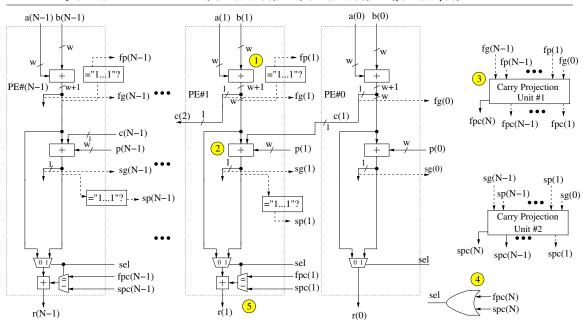

| 3.2 | Hybrid radix- $2^w$ carry save adder with the carry projection unit based on                                     |     |  |  |  |

|-----|------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

|     | parallel prefix network (PPN). Design X - Design I is based on Kogge-Stone                                       |     |  |  |  |

|     | PPN and Design II is based on Brent-Kung PPN                                                                     | 55  |  |  |  |

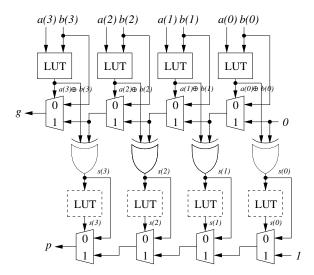

| 3.3 | Implementation of the generate/propagate logic using fast carry chains and                                       |     |  |  |  |

|     | LUTs of Xilinx FPGAs                                                                                             | 58  |  |  |  |

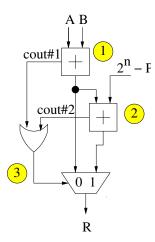

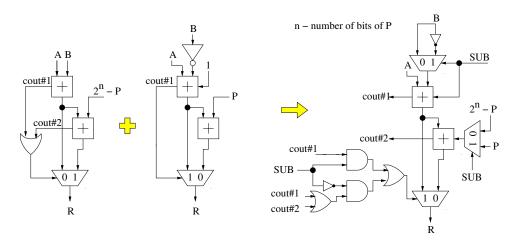

| 3.4 | Modular adder based introduced in [20]                                                                           | 59  |  |  |  |

| 3.5 | Modular adder based on the hybrid adder                                                                          | 60  |  |  |  |

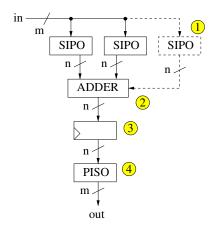

| 3.6 | Test circuit for addition and modular addition                                                                   | 61  |  |  |  |

| 4.1 | Modular adder/subtractor - high level block diagram                                                              | 74  |  |  |  |

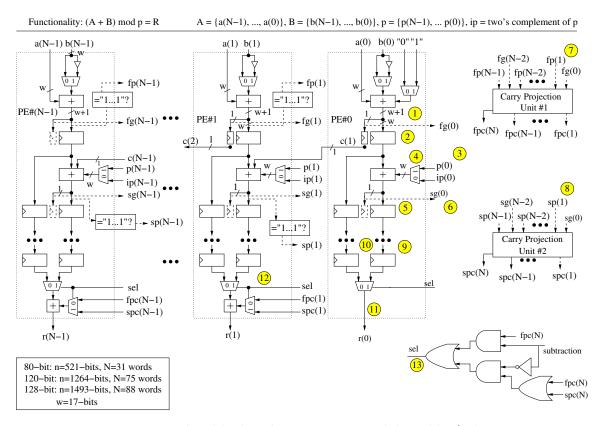

| 4.2 | Pipelined high-radix carry save modular adder/subtractor                                                         | 74  |  |  |  |

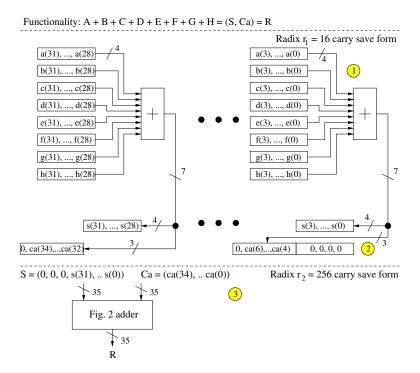

| 4.3 | High-radix carry save multi-operand adder                                                                        | 77  |  |  |  |

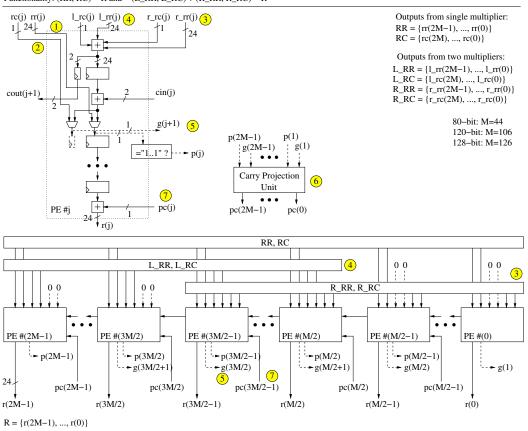

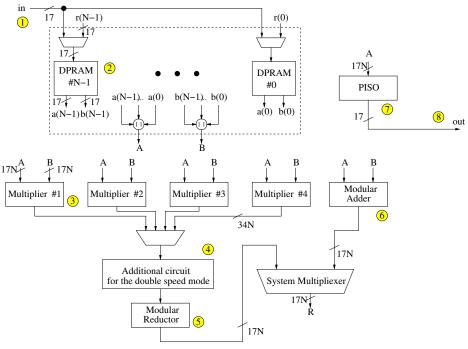

| 4.4 | Block diagram of a multiplier based on 24x17 DSP units                                                           | 79  |  |  |  |

| 4.5 | Additional circuit for the multiplier double speed mode support. ( $L\_RR =$                                     |     |  |  |  |

|     | $(RR \ll \frac{24 \cdot M}{2}), LRC = (RC \ll \frac{24 \cdot M}{2}), \text{ for (RR, RC) from left multiplier)}$ |     |  |  |  |

|     | and $(L\_RR = RR, L\_RC = RC, \text{ for (RR, RC) from right multiplier)}$                                       | 80  |  |  |  |

| 4.6 | Block diagram of Barrett reduction for Solinas primes                                                            | 85  |  |  |  |

| 5.1 | Hierarchy of functions in pairing-based cryptosystems                                                            | 93  |  |  |  |

| 5.2 | Top level block diagram of pairing coprocessor                                                                   | 110 |  |  |  |

| 6.1 | Timeline of the major cryptographic competitions                                                                 | 127 |  |  |  |

| 6.2 | Relation between design flows of Altera and Xilinx and heuristic algorithms                                      |     |  |  |  |

|     | in ATHENa                                                                                                        | 131 |  |  |  |

| 6.3 | Dependency between requested and achieved frequency for combined opti-                                           |     |  |  |  |

|     | mization targets                                                                                                 | 135 |  |  |  |

| 6.4 | ATHENa GMU_optimzation_1 method for Xilinx devices                                                               | 136 |  |  |  |

| 6.5 | ATHENa GMU_optimzation_1 method for Altera devices                                                               | 137 |  |  |  |

| 6.6 | Relative improvement of results from using ATHENa Virtex 5, 256-bit vari-                                        |     |  |  |  |

|     | ants of hash functions. Ratios of results obtained using ATHENa suggested                                        |     |  |  |  |

|     | options vs. default options of FPGA tools. [21]                                                                  | 138 |  |  |  |

Abstract

DEVELOPMENT AND BENCHMARKING OF NEW HARDWARE ARCHITECTURES

FOR EMERGING CRYPTOGRAPHIC TRANSFORMATIONS

Marcin Rogawski, PhD

George Mason University, 2013

Dissertation Director: Dr. Kris Gaj

Cryptography is a very active branch of science. Due to the everlasting struggle be-

tween cryptographers, designing new algorithms, and cryptanalysts, attempting to break

them, the cryptographic standards are constantly evolving. In the period 2007-2012, the

National Institute of Standards and Technology (NIST) held a competition to select a new

cryptographic hash function standard, called SHA-3. The major outcome of this contest,

apart from the winner - Keccak, is a strong portfolio of cryptographic hash functions. One

of the five final SHA-3 finalists, Grøstl, has been inspired by Advanced Encryption Stan-

dard (AES), and thus can share hardware resources with AES. As a part of this thesis,

we have developed a new hardware architecture for a high-speed coprocessor supporting

HMAC (Hash Message Authentication Code) based on Grøstl and AES in the counter

mode. Both algorithms provide efficient hardware acceleration for the authenticated en-

cryption functionality, used in multiple practical security protocols (e.g., IPSec, SSL, and

SSH). Our coprocessor outperforms the most competitive design by Jarvinen in terms of

the throughput and throughput/area ratio by 133% and 64%, respectively.

Pairing-based cryptography has emerged as an important alternative and supplement to

traditional public key cryptography. Pairing-based schemes can be used for identity-based

الغ للاستشارات

encryption, tripartite key exchange protocols, short signatures, identity-based signatures, cryptanalysis, and many other important applications. Compared to other popular public key cryptosystems, such as ECC and RSA, pairing-based schemes are much more computationally intensive. Therefore, hardware acceleration based on modern high-performance FPGAs is an important implementation option. Pairing-schemes over prime fields are considered particularly resistant to cryptanalysis, but at the same time, the most challenging to implement in hardware. One of the most promising optimization options is taking advantage of embedded resources of modern FPGAs. Practically all FPGA vendors incorporate in modern FPGAs, apart from basic reconfigurable logic blocks, also embedded components, such as DSP units, Fast Carry Chain Adders, and large memory blocks. These hardwired FPGA resources, together with meticulously selected prime numbers, such as Mersenne, Fermat, or Solinas primes, can serve as a basis of an efficient hardware implementation. In this work, we demonstrate a novel high-speed architecture for Tate pairing over prime fields, based on the use of Solinas primes, Fast Carry Chains, and DSP units of modern FPGAs. Our architecture combines Booth recoding, Barrett modular reduction, and the high-radix carry-save representation in the new design for modular multiplication over Solinas primes. Similarly, a low-latency modular adder, based on high-radix carry save addition, Fast Carry Chains, and the Kogge-Stone architecture, has been proposed. The modular multiplier and adder based on the aforementioned principles have been used as basic building blocks for a higher level application - a high-speed hardware accelerator for Tate pairing on twisted supersingular Edwards curves over prime fields. The fastest version of our design calculates Tate pairing at the 80, 120 and 128-bit security level over prime fields in 0.13, 0.54 and 0.70 ms, respectively. It is the fastest pairing implementation over prime fields in the 120-128-bit security range.

Apart of the properly designed architectures for cryptographic algorithms, one more ingredient contributes to the success of a hardware coprocessor for any application - an

electronic design automation software and its set of options. Concerning this issue, Cryptographic Engineering Research Group (CERG) at Mason has developed an open-source environment, called ATHENa (Automated Tool for Hardware Evaluation), for fair, comprehensive, automated, and collaborative hardware benchmarking and optimization of algorithms implemented in FPGAs. One of the contributions of this thesis is the design of the heart of ATHENa: its most efficient heuristic optimization algorithm, called *GMU\_Optimization\_1*. As a basis of its development, multiple comprehensive experiments have been conducted. This algorithm has been demonstrated to provide up to 100% improvement in terms of the throughput to area ratio, when applied to 14 SHA-3 Round 2 candidates. Additionally, our optimization strategy is applicable to the optimization of dedicated hardware in any other area of science and engineering.

**Keywords:** Cryptography, High-performance hardware architectures, Pairing-based cryptography, modular arithmetic, authenticated encryption, heuristic methods for electronic design automation.

#### Chapter 1: Introduction

#### 1.1 Motivation

New directions in Cryptography, namely Public Key Cryptography (PKC) discovery in 1976 by Diffie and Hellman [23], were introduced to solve the security problems such as confidentiality, authenticity, integrity, non-repudiation and also secure key exchange during communications in insecure networks. The first practical realization of PKC was RSA, proposed by Ron Rivest, Adi Shamir and Len Adleman in 1977 [24].

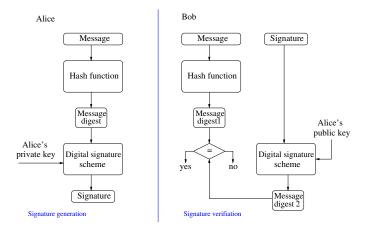

A digital signature scheme is a mathematical algorithm for demonstrating the authenticity of a digital message. Typically, digital signature is represented by a string of bits which is dependent on some secret known only to the signer (known as the signer's private key) and the content of the document being signed. Signatures have to be easily verifiable in case of a dispute about the origin of the document. An unbiased third party should be able to resolve this issue undeniably, without accessing signer's private key. Digital signatures are used to implement three major security services: authentication, integrity, and non-repudiation. Digital signatures are based on two main cryptographic transformations:

- a hash function, which takes an arbitrary size message and transforms it into a fixedsize hash value (also known as message digest), and

- a digital signature scheme, which takes: a private key of the signer and a hash value of the message to generate digital signature, and a public key of the signer, a hash value of the message, and a digital signature to verify whether a given digital signature is valid.

There are several security requirements for both algorithms: a hash function must be

Figure 1.1: Digital signature generation and verification

irreversible and collision free and a digital signature scheme must be computationally infeasible to break. Digital signatures, key exchange and encryption schemes are used in a wide variety of Internet security protocols, such as Secure Socket Layer (SSL), Internet Protocol Security (IPSec), Domain Name System Security Extensions (DNSSec), Secure Border Gateway Protocol, etc. For example SSL uses digital signatures to authenticate secure web servers to their clients all over the world.

In IPSec the most important handshaking mode for the Internet Key Exchange protocol, apart from the key exchange support, is also based on a digital signature concept. The Domain Name System Security Extensions (DNSSec) is a new protocol for binding IP addresses and their domain names. The DNSSec requires digital signatures to provide strong authentication within the chain of trust. An aggregate signature is useful for reducing the size of certificate chains and for reducing message size in secure routing protocols such as Secure Border Gateway Protocol. These are just a few high level protocols, which are the basis of the security of any electronic information and in particular digital fund transfers used in on-line shopping, bank transactions and e-documents circulation.

For cryptographic hash functions, two families of algorithms, commonly referred to as SHA-1 and SHA-2, have been standardized by NIST, as described in the Federal Information

Processing Standard number 180 (the most current version is denoted FIPS-180-3). This standard defines the following variants of both families: SHA-1, SHA-2/224, SHA-2/256, SHA-2/384 and SHA-2/512. In 2005, a significant attack against SHA-1 was published [25]. A similarity between the SHA-1 and the SHA-2 specification raises the question about the possibility of extending this recently discovered attack to threaten the remaining four versions of Secure Hash Algorithm. This potential weakness in SHA-2 can affect the security of digital signature schemes based on this algorithm and finally, may undermine the robustness of cryptographic services using these signatures.

The National Institute of Standard and Technology (NIST) developed a memorandum with minimum key sizes for different security levels and for different underlying technologies. A sensitive data which is required to be protected at least until 2030 must be guarded by hash function SHA-2 with 256-bits output (SHA-3 will be an alternative solution), Advanced Encryption Standard with 128-bit key, and by digital signature schemes based on RSA and ECC technology with 3072 and 256-bits operands, respectively. The European Network of Excellence for Cryptology (ECRYPT) released similar recommendation for key sizes. However, it is stated in their work that the recommendations may need to be revised taking into account more efficient attacks that are known to exist for discrete logarithm over binary fields. The National Security Agency released the Fact Sheet NSA Suite B Cryptography where the aforementioned requirements were confirmed, but it also recommends a transition into elliptic curve systems instead of classical public key technology. This document provides the recommendation for the underlying modular arithmetic, the prime fields must be used, instead of binary and ternary fields.

Digital signature schemes and other cryptographic algorithms have been successfully implemented on a large spectrum of platforms: starting from dedicated smart card chips, through 8-bit microcontrollers, 32 and 64-bit microprocessors and finally, on high performance application specific security processors.

In general, software solutions demonstrate:

• relatively low performance, and large power and energy consumption,

- difficulty in terms of generation truly random keys,

- vulnerability to software malware and a big class of side channel attacks (e.g. timing attacks, cache attacks, etc.)

Contrary to software implementations, Application Specific Integrated Circuits (ASIC technology) require long development time and a very expensive computer-aided design (CAD) software. Moreover, after fabrication of an ASIC device, the designers cannot introduce any upgrades to the implementation. ASIC-based solution are very costly in low volumes, they require extensive and expensive testing, and the fabrication mistakes are unrecoverable.

Cryptographic services, based on digital signature schemes, key exchange and encryption schemes, are at the beginning of a new era. Novel basic cryptographic transformations, based on the cutting edge underlying technology, for the the aforementioned schemes were developed recently. They offer not only higher security, but also a set of new properties. It is possible to apply them to a big range of new applications.

In case of cryptographic hash functions NIST has started a public competition for a new SHA-3 function. Out of initial 51 candidates, only 5 algorithms were selected to the 3rd and final round: BLAKE, Grøstl, JH, Keccak and Skein. In December 2012 Keccak has been announced the winner of the contest.

Four major criteria were taken into account in the evaluation of these candidates are:

- security,

- performance in software,

- performance in hardware, and

- flexibility.

While security is commonly recognized as the most important evaluation criterion, it is also a measure that is most difficult to evaluate and quantify, especially during a relatively short period of time reserved for the majority of contests. So far all five SHA-3 final round

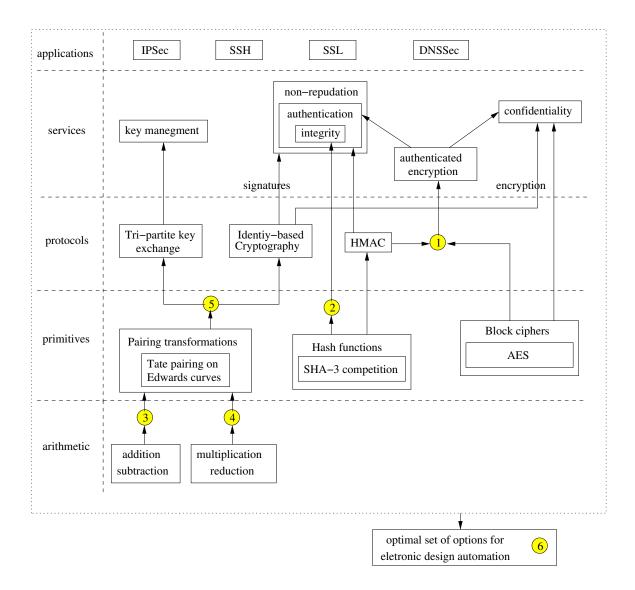

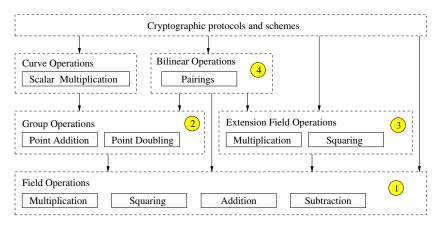

Figure 1.2: Hierarchical model of Cryptographic applications. Major contribution of this research marked with points 1-6.

candidates demonstrate higher security margin than SHA-2 algorithm. Comprehensive analysis of hardware and software implementations of final candidates was conducted by multiple cryptographic engineering research groups all over the world. These studies show potential throughput gain over solutions based on current standard. On the other hand they also show that SHA-3 will be more expensive in terms of area used in hardware.

Pairing-based schemes can be used as basic building blocks for such high level protocols like:

- identity-based encryption (identity used as a key for encryption),

- identity-based signatures (identity used as a key for signing),

- triparite key exchange (one round of computations allow the key agreement between three parties)

- group signatures (a method for allowing a member of a group to anonymously sign a message on behalf of the group),

- blind signatures (the content of a message is disguised before it is signed),

- aggregate signatures (given n signatures applied to n messages from n users, it is possible to aggregate all these signatures into a single signature which size is independent of the number of users).

This novel technology bridges the gap between the classical Public Key and the Elliptic Curve Cryptography.

In general pairing algorithms take two arguments—two elliptic curve points P and Q from two different algebraic groups  $G_1$  and  $G_2$  and it produces an element of the third algebraic group  $G_T$ .

The most important properties of these  $G_1 \times G_2 \to G_T$  functions are:

- bilinearity  $\forall a, b \in \mathbb{Z}_p$ :  $e(aP, bQ) = e(P, Q)^{ab}$ ,

- non-degeneracy (function e(P,Q) never returns '1')

• and efficiency in computations.

Different types of pairing functions were developed in the past, but for the prime fields the most practical are the Tate and the Optimal Ate pairing transformations. Both of them are based on the concept of iterative calculation (Miller's algorithm [27]) of a new value of pairing function for a given evaluation point, and a calculation of a new evaluation point. The Tate pairing is most efficient for the ordinary Elliptic Curves and the Optimal Ate pairing for a special class of - so called Barreto-Naehrig (B-N) curves.

In 2007 a new form of elliptic curves was discovered, so called Edwards curves. The advantages of this new form are:

- the fastest reported in the literature unified procedure for addition and doubling points,

- it is possible to embed those basic operations together with Tate pairing function evaluation,

- twisted Edwards curves with extended projective coordinates are very easy for parallelization and in fact potentially the most hardware-friendly.

In recent years implementations of cryptography on FPGAs became a popular subject in academic research and in commercial security products. Historically, FPGAs have been slower, less energy efficient and generally achieved lower physical security than their fixed ASIC counterparts. Advantages include the ability to re-program in the field to fix bugs, a shorter time to market, and lower non-recurring engineering costs. Some FPGAs have the capability of partial re-configuration that lets one portion of the device be re-programmed while other portions continue running.

In comparison to software implementations, FPGA-based cryptographic systems are faster in majority of cases, they consume less power and they offer temper resistance and overall higher security. In favor of general-purpose microprocessors software implementations have even higher flexibility and smaller development costs. Both software and FPGA

developers have an access to freely available design tools. One of the most important reasons why FPGA-based cryptographic systems are successful is the specific nature of cryptographic market and the requirements for commercial products in this sensitive area. In the developed countries, the governments require that cryptographic products pass certification process, They also demand to be involved in the design process of those solutions and to have an access to their source codes. This general policy makes the cryptographic product's market suffer from a lack of global companies. In case of relatively small companies an ideal solution for a cryptographic system, which requires high performance, capability for upgrades, low volume, and a short time to market, are the FPGA devices.

This thesis aims to answer a question: Can the recent advances in the theory of Elliptic Curves and pairing functions (namely the invention of Edwards Curves and its application to the Tate pairing) and in the theory of hash functions (namely the development of the SHA-3 standard) be exploited to develop the most efficient FPGA-based hardware architecture for the most important cryptographic services, outperforming all previously known architectures with equivalent security?

#### 1.2 Summary of research contributions

#### 1.2.1 Novel hardware accelerator for authenticated encryption

SHA-3 finalist, hash function Grøstl, has been inspired by the Advanced Encryption Standard (AES). This unique feature can be exploited in a large variety of practical applications (Fig. 1.2 pt. 1). In order to have a better picture of the Grøstl-AES computational efficiency (high-level scheduling, internal pipelining, resource sharing, etc.), we designed a high-speed coprocessor for the Grøstl-based HMAC and AES in the counter mode. This coprocessor offers high-speed computations of both authentication and encryption with relatively small penalty in terms of area and speed when compared to the authentication (original Grøstl circuitry) functionality only. It is almost certain that the highest quality cryptographic

algorithms, like SHA-3 finalists, will find their niche applications.

For example: this coprocessor outperforms similar hardware accelerator proposed in [1] for both IPSec modes: IP Encapsulating Security Payload (ESP) and Authentication Headers (AH) by 64% and 8%, respectively. In case of the relatively rare the ESP's encryption mode only, the coprocessor from [1] is better by 44% as compared to our results.

Extracts of this work were published as joint work with Ekawat Homsirikamol and Kris Gaj [28] and [29]

#### 1.2.2 An adaptation of the T-box method to the AES-like hash functions

Joan Daemen, co-inventor of arguably two most important cryptographic standards - Advanced Encryption Standards (AES) and Secure Hash Algorithm (Keccak), proposed in his PhD thesis, a provably secure method of building cryptographic transformation, the Wide Trail Strategy. A block cipher SHARK was build upon this principle and a new, so called Table-box method for very efficient implementation of this algorithm was published in 1996. This mathod allows to redefine the round structure in a such a way, that it is friendly for FPGA memory blocks. Several researchers have proposed hardware coprocessors for AES based on the T-box method, which are the fastest [30], the most efficient [31], and implementation attacks resistant [32]. In our research we concentrated on the Wide Trail Strategy progeny, the AES-based hash functions: ECHO, Fugue, Grøstl-0 and SHAvite-3 ((Fig. 1.2 pt. 2)). The efficiency of the hardware accelerators for aforementioned algorithms have been improved up to 49, 173, 424 and 262 %, respectively. In this work, we have extended our work for SHA-3 finalist, Grøstl. We have demonstrated, the best hardware accelerator in terms throughput/area ratio, reported in open literature.

Extracts of this work were published as joint work with Rabia Shahid, Malik Umar Sharif and Kris Gaj [33] and [34].

# 1.2.3 A novel, adder/subtractor for thousand bit and more using fast carry chains of modern FPGAs

We have demonstrated a new, low latency, FPGA-oriented, hybrid adder ((Fig. 1.2 pt. 3)). This adder efficiently combines the ideas of high-radix carry save addition based on the fast carry chains, available on modern FPGA devices, and the parallel prefix network. The implementation results reveals that this hybrid adder has a great potential for the addition and modular addition of the long-size integers.

For example, our adder outperform, in terms of latency  $\cdot$  area, both classical designs: Kogge-Stone and Brent-Kung, on 1024, 2048 and 4096-bits addition up to 50, 38 and 35%, respectively. At the same time, in terms of latency, our design is very competitive to the both, commonly accepted, as the fastest adders in open literature.

Moreover, our hybrid high-radix carry save adder with carry projection unit based on parallel prefix network have been applied to the 1024-bit modular addition circuit. The implementation results on modern FPGA devices have proven that in terms of latency, area and latency · area product, for Altera devices, have been improved over both classical designs, on average 15, 40 and 55%, respectively. In case of Xilinx devices these numbers were 50, 45 and 70%, respectively.

Extracts of this work were published as joint work with Kris Gaj and Ekawat Homsirikamol [35].

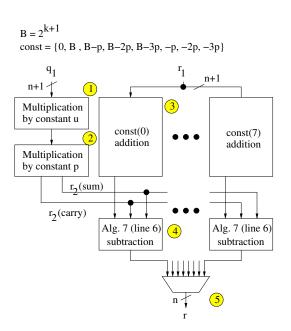

## 1.2.4 New approach to arithmetic based on the Solinas primes for Pairingbased Cryptography

A well known shortcut for a modular multiplication modulo a Mersenne number  $(2^k - 1)$ , performing modular reduction without integer division has been generalized by Jerome A. Solinas, a researcher from National Security Agency (NSA). The prime numbers generated using his method and the fast arithmetic developed for them have been named after him.

These concepts have been such a important invention, that a big class of Solinas prime numbers and their efficient arithmetic have been widely accepted, recommended and in fact they became a part of a elliptic curved-based digital signature standard.

The aforementioned reduction technique is not applicable for all Solinas primes, in particular for those which are used in Pairing-based Cryptography.

First, we have demonstrated that Solinas primes can benefit from the modified Barrett reduction algorithm and then we have proposed conditions for efficient arithmetic based on those primes. Next, we have optimized a grid method for multiplication to the geometry of the digital signal processing blocks (DSP units), embedded in the structure of modern FPGA devices.

This simple, thus very flexible design can give us some unique features - e.g.: it allows to speed up single multiplication by using two multipliers. This special feature is especially attractive in case of n multiplications, m available multipliers, and n dividing m. (e.g.: a coprocessor build upon four multipliers, and a single iteration of the final exponentiation algorithm in case of supersingular curves with embedding degree k=2 requires 2 multiplications).

Finally, we have combined both concepts: grid multiplication method optimized for FPGAs and the Barrett reduction for Solinas primes, and as a result we have obtained, optimal, modular multiplier for pairing-friendly Solinas primes (Fig. 1.2 pt. 4).

Extracts of this work were published as joint work with Kris Gaj [36]

#### 1.2.5 Novel hardware architectures for pairing on Edwards curves

We are going to demonstrate the first and the only to date, a high speed hardware accelerator for the Tate pairing on twisted supersingular Edwards curves over prime fields (Fig. 1.2 pt. 5). Our hardware architecture is based on the set of algorithms presented in [37]. It can be used directly to support emerging pairing-based protocols. This coprocessor was built upon the hardware architectures proposed for Solinas primes and the hybrid high-radix carry save

and parallel prefix network adder. We demonstrate that combining aforementioned concepts together with novel method for optimizations for final exponentiation, tight pipelining for optimal number of processing units can improve an alternative software implementation by a factor of 50 for three different security levels.

Finally, we have demonstrated, that even though Edwards curves were not optimized for pairing, they present an interesting alternative to pairing friendly Barreto-Naehrig curves. The implementation results, the hardware accelerator based on Stratix V, are elevating it, to the top of the list of the fastest, to date, pairing solution over prime fields in a security range 120-128-bits.

Extracts of this work were published as joint work with Kris Gaj [36]

# 1.2.6 A heuristic strategy for FPGA-oriented electronic design automation

In 2010 Cryptographic Engineering Research Group have introduced an open-source environment, called ATHENa for fair, comprehensive, automated, and collaborative hardware benchmarking of algorithms belonging to the same class. Apart from this primary use for a fair evaluation of functionally equivalent digital system designs targeting FPGAs, a major goal for this design automation system is an efficient search for the best set of options for a given optimization criterium. In this work we have demonstrated the design rationale of the most successful heuristic optimization algorithm, the ATHENa's heart,  $GMU_Optimization_1$  (Fig. 1.2 pt. 6). This method helps to improve up to 100% throughput/area ratio of hardware accelerators for major FPGA vendors and for functionally different digital circuits (e.g.: modular arithmetic, pairing systems, hash function and block ciphers).

Extracts of this work were published as joint work with Kris Gaj, Jens-Peter Kaps, Venkata Amriamieni, Ekawat Homsirikamol, and Benjamin Brewster in [38]. The heuristic method "GMU\_Optimization\_1" helped to achieve the best to date hardware implementation

$results \ in \ multiple \ our \ papers, \ including \ [39], \ [21], \ [40], \ [33], \ [28], \ [36] \ and \ [29].$

## Part I

High-performance hardware architectures supporting confidentiality and integrity

## Chapter 2: High-Throughput hardware architectures of AES-like Cryptographic hash functions

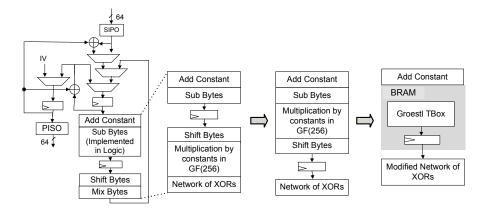

This chapter presents two unique hardware architectures for coprocessors supporting AES-like hash functions. First, we demonstrate an adaptation of T-table (also called T-box) method for the AES-based family of hash functions. We have used SHA-3 finalist, Grøstl, to show that this method gives the best throughput/area ratio for hardware implementations of this important class of cryptographic transformations. Finally, we have demonstrated how to use Grøstl and AES cipher similarities and convert them into a coprocessor which offers high-speed computations of both authentication and encryption.

#### Contents

| 2.1 | Introduction and motivation                                                  | 14 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | Previous work                                                                | 17 |

| 2.3 | ${\bf Table-based\ method\ extension\ for\ AES-like\ cryptographic\ trans-}$ |    |

|     | formations (Grøstl case)                                                     | 22 |

| 2.4 | Hardware architecture for the authenticated encryption based                 |    |

|     | on Grøstl and AES                                                            | 28 |

#### 2.1 Introduction and motivation

In the period 2007-2012, the National Institute of Standards and Technology (NIST) was holding a hash competition [41] to select a new cryptographic hash function standard, called

SHA-3, for the purpose of superseding the functions in the SHA-2 family [42]. Performance in hardware has been one of the major factors taken into account by NIST in the evaluation of Round 2 and Round 3 candidates during the SHA-3 competition [41], [43], [44]. This factor was particularly important in the final round of the contest, because the algorithms qualified to this round were not very likely to have any significant security weaknesses.

On October 2, 2012, Keccak [45] has been announced to be the winner of the NIST hash function competition [46]. This algorithm has demonstrated medium speed in software implementations [47], [48], and the best results in terms of hardware efficiency for both single stream [43] and multiple streams of data in hardware implementations [39].

Beyond any doubt, cryptographic standards for block ciphers: AES [49] and 3DES [50] and hash functions SHA-2 [42] and newly selected future standard - Keccak [45] are the most important crypto-algorithms for both Academia and Industry.

The SHA-3 competition was very similar in many aspects to the AES competition [51]: both were open and fully transparent contests, organized by NIST. They have received relatively big attention from the cryptographic community and the final result was announced after multiple years of intensive investigations in the area of security, hardware and software performance. The major outcome from both contests seems to be as well as very similar a strong portfolio of cryptographic transformations.

Apart from the winner of AES contest, almost all finalists have been either implemented in different commercial products (e.g.: [52], [53], [54]) or they were patented [55]. It is almost certain that the highest quality cryptographic algorithms, like SHA-3 finalists, will find their niche applications.

The main objective of almost all SHA-3 related studies was to evaluate all candidates using a uniform approach, and therefore the unique features of each and every function were not deeply investigated.

There are relatively few works that discuss any distinctive hardware architectures for the SHA-3 candidates. A coprocessor supporting Skein in tree hashing mode was presented in [56]. Common architectures of the block cipher AES and the Round 2 versions of Grøstl-0

and Fugue algorithms were reported in [1]. Recently, a high-speed AES-Grøstl architecture was also reported in [57].

A compact implementation of the block cipher Threefish and the Round 3 hash algorithm Skein was demonstrated in [58]. Three outstanding low-area, resource-sharing oriented coprocessors, for combinations: Round 3 version of Grøstl/AES and ECHO/AES were proposed, designed and discussed in [59], [60] and [61], respectively.

The similarities between AES and Grøstl (or any other AES-like hash function - Fig. 2.1) lead us to two, unique and important architectures.

First of all, the majority of AES hardware accelerators implement a single round in a straightforward way or using loop-unrolling, pipelining techniques for FPGAs, utilizing a vast amount of user logic elements. This approach, based on a traditional configurable logic utilization, help to maintain platform independence, and therefore it does not exploit the full potential of modern FPGA devices. Contrary, the T-table method, described in [62], Sec. 4.2 enables the memory-oriented re-definition of AES round, and it eventually leads to the highly efficient hardware architecture of AES.

To the best of our knowledge, our work [33] was the very first one, which demonstrated a T-table-based representation of Grøstl-0 (and also ECHO, Fugue and SHAvite-3).

Second important implication of this compatibility between the current encryption standard, AES and the whole family of AES-derived hash function is their joint use for authenticated encryption. A typical application for such cryptographic service could be Secure Socket Layer [63], Transport Layer Security [64], Secure Shell [65] and Internet Protocol Security [66–68].

#### The rest of this chapter is organized as follows:

In Section 2.2 we discuss relevant previous work. Section 2.3 is devoted to the description of the T-table architecture of Grøstl. Section 2.4 demonstrates the design of a hardware coprocessor for authenticated encryption.

#### 2.2 Previous work

#### 2.2.1 Grøstl in SHA-3 competition

In January 2011, Grøstl team published tweaks to their specification of Grøstl [69], [17]. An algorithm described by the original Grøstl specification [70] has been renamed to Grøstl-0, and the tweaked version of Grøstl, described by the revised specification [17], is from this point-on called Grøstl. The proposed tweaks are aimed primarily at the increase in the algorithm resistance to cryptanalysis [69]. This increased resistance in security, typically comes together with some limited penalty in terms of performance in hardware [71].

Grøstl-0 has been implemented by several groups in FPGAs and ASICs [43]. In this chapter, we focus on implementations targeting FPGAs and optimized for high speed rather than low area. High-speed implementations of Grøstl-0 typically use two major architectures. In the first architecture, reported first in [70], permutations P and Q are implemented using two independent units, working in parallel. We call this architecture parallel architecture. In the second architecture, introduced in [72], the same unit is used to implement both P and Q. This unit is composed of two pipeline stages that allow interleaving computations belonging to permutations P and Q. We call this architecture quasi-pipelined architecture, as it is based on the similar principles as the quasi-pipelined architectures of SHA-1 and SHA-2 reported in [73], [74]. The details of the quasi-pipelined architecture of Grøstl-0 are described in [72] (Section 9), [75] (Section 3.8) and [76] (Section V).

An analysis of the influence of the Round 3 tweaks in Grøstl on the performance of this algorithm in FPGAs was conducted in [71]. Comprehensive hardware evaluation across multiple architectures for all SHA-3 finalists, including Grøstl, was investigated in [39] and [81]. The implementation results of hardware architectures, for a single stream of data, in both variants of Grøstl-256 are summarized in Table 2.1.

Table 2.1: Results of Implementations for High-Speed Architectures of Grøstl-256, using Xilinx Virtex 5 FPGAs.

| Source                   | Memory | Frequency     | Throughput | Area    | Throughput/Area |

|--------------------------|--------|---------------|------------|---------|-----------------|

|                          | [BRAM] | [MHz]         | [Mbps]     | [Slice] | [Mbps/Slice]    |

|                          | Gr     | østl-0 - Roun | d 2        |         |                 |

| Gauravaram et al. [70]   | N/A    | 200.7         | 10276      | 1722    | 5.97            |

| Jungk et al. [76]        | 17     | 295.0         | 7552       | 1381    | 5.46            |

| Shahid et al. [40]       | 48     | 250.0         | 6098       | 1188    | 5.13            |

| Homsirikamol et al. [75] | 0      | 323.4         | 7885       | 1597    | 4.94            |

| Gaj et al. [21]          | 0      | 355.9         | 8676       | 1884    | 4.61            |

| Matsuo et al. [77]       | 0      | 154.0         | 7885       | 2616    | 3.01            |

| Baldwin et al. [78]      | 0      | 101.3         | 5187       | 2391    | 2.17            |

| Kobayashi et al. [79]    | 0      | 101.0         | 5171       | 4057    | 1.27            |

| Guo et al. [80]          | 0      | 80.2          | 4106       | 3308    | 1.24            |

| Baldwin et al. [78]      | 0      | 101.3         | 3242       | 2391    | 1.36            |

| Baldwin et al. [78]      | 0      | 78.1          | 2498       | 2579    | 0.97            |

|                          | G      | røstl - Round | l 3        |         |                 |

| Sharif et al. [33]       | 18     | 226           | 5524       | 1141    | 4.84            |

| Gaj et al. [81]          | 0      | 251           | 6117       | 1795    | 3.41            |

| Homsirikamol et al. [39] | 0      | 249           | 6072       | 1912    | 3.18            |

| Homsirikamol et al. [39] | 0      | 158           | 8081       | 2591    | 3.12            |

#### 2.2.2 T-box method

Joan Daemen, in his PhD thesis [2], proposed the Wide Trail Strategy. It is a method of constructing highly efficient block ciphers, which are provably secure against major cryptanalytical attacks.

This Wide Trail Strategy became a design rationale of several cryptographic transformations (Fig. 2.1). Most of them demonstrate not only the hardware-software efficiency and flexibility, but also an elegance in their description.

Fig. 2.1 presents the timeline development of the aforementioned class of cryptographic transformations.

In paper [3], Shark ((Fig. 2.1 pt. 4) pt. 1) was proposed together with its efficient implementation methods. This paper demonstrated how to combine several simpler mathematical transformations into one operation equivalent to a round. This method was named table implementation, T-table or T-box implementation.

To the best of our knowledge, the first attempt of the adoption of this method for the hardware implementation of the AES round was proposed by Fischer and Drutarovsky in

pre-AES work **AES NESSIE** SHA-3 (2007-2012)(1997-2000)(2000-2003)(1995-1997)Hierocrypt Shark Khazad 1 Anubis Shavite-3 Grand Cru **ECHO** Rijndael (AES) Fugue Q Groestl Square Serpent JH Twofish Crypton

Joan Daemen PhD's Wide Trail Strategy progeny - AES family

BaseKing/3way

Figure 2.1: Wide Trail Strategy family of cryptographic transformations was defined in [2]. Based on this strategy several algorithms have been invented: Shark [3], Square [4], BaseKing [2], Rijndael-AES [5], Serpent [6], Twofish [7], Crypton [8], Hiercorypt [9], Khazad [10], Anubis [11], GrandCru [12], Q [13], Noekeon [14], ECHO [15], Fugue [16], Grøstl [17], SHAvite-3 [18] and JH [19]

block ciphers

Noekeon

hash functions

[31] (Fig. 2.1 pt. 2). Contrary to that implementation the design, described by Drimer et al. in [30], maps the complete AES data path onto embedded elements contained in Virtex-5 FPGAs. This strategy provides most savings in logic and routing resources and results in the highest data throughput on FPGAs reported in open literature.

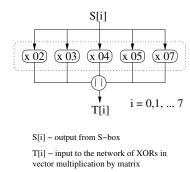

Taking into account the fact that the whole AES family (Fig. 2.1) is built upon similar principles, several implementational nuances can be inherited. We have proposed architectural improvements, using aforementioned technique, for block cipher Hierocrypt in [34] (Fig. 2.1 pt. 3) and hash functions: ECHO, Fugue, Grøstl-0 and SHAvite-3 in [33] (Fig. 2.1 pt. 4). Table 2.2 summarizes the geometry of the T-tables reported in open literature.

Table 2.2: Table-based hardware architectures of cryptographic transformations. T-box geometry AxB is defined by A-bit address space and B-bit words.

| algorithm     | T-box size | source                                  |  |  |

|---------------|------------|-----------------------------------------|--|--|

| Block Ciphers |            |                                         |  |  |

| AES           | 8x32       | Fischer et al. [31], Drimer et al. [30] |  |  |

| Hierocrypt-3  | 8x32       | Rogawski [34]                           |  |  |

|               | Hasl       | r Functions                             |  |  |

| Grøstl-0      | 8x40       | Shahid et al. [40]                      |  |  |

| Fugue         | 8x24, 8x32 | Shahid et al. [40]                      |  |  |

| ECHO          | 8x32       | Shahid et al. [40]                      |  |  |

| SHAvite-3     | 8x32       | Shahid et al. [40]                      |  |  |

| Grøstl        | 8x40       | ch. 2.3                                 |  |  |

#### 2.2.3 Resource sharing

The idea of hardware resource sharing is very practical and especially attractive in industrial applications. Several companies offer so called all-in-one cryptographic solutions. For example, [82] and [83] offer customized cores, including sophisticated AES core, which supports 128, 192 and 256-bit main key and several different operational modes in a single chip. This concept was also investigated by academia: shared MD5 and SHA-1 implementation was described in [84–86], MD5 implemented together with RIPEMD-160 was reported in [87], a combined SHA-1, MD-5 and RIPEMD-160, core was discussed in [88]. Fugue with

Table 2.3: Hardware architectures supporting authenticated encryption at 128-bit security

| Source                                                                           | Algorytms                                                                            | FPGA           | Frequency     | Area         | Throughput     | Throughput/Area   |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|---------------|--------------|----------------|-------------------|--|--|

|                                                                                  |                                                                                      |                | [MHz]         | [Slice/LE]   | [Mbps]         | [Mbps/(Slice/LE)] |  |  |

|                                                                                  |                                                                                      | Balance        | ed designs    |              |                |                   |  |  |

| Rogawski et al. [28]                                                             | Grøstl-0 and AES                                                                     | Cyclone III    | 159.9         | 23039        | 2640           | 0.12              |  |  |

| Järvinen [1]                                                                     | Grøstl-0 and AES                                                                     | Cyclone III    | 53.4          | 13723        | $956^{1}$      | 0.07              |  |  |

| Järvinen [1]                                                                     | Fugue and AES                                                                        | Cyclone III    | 59.8          | 4875         | $273^{1}$      | 0.06              |  |  |

|                                                                                  |                                                                                      | Low are        | ea designs    |              |                |                   |  |  |

| At et al. [90]                                                                   | Grøstl and AES <sup>2</sup>                                                          | Virtex-6       | 393           | $169^{4}$    | $64.6^{1}$     | 0.38              |  |  |

| Beuchat et al. [91]                                                              | ECHO and AES <sup>3</sup>                                                            | Virtex-6       | 397           | $155^{5}$    | $62.6^{1}$     | 0.40              |  |  |

| At et al. [58]                                                                   | Skein and Twofish                                                                    | Virtex-6       | 276           | $132^{5}$    | $40.0^{1}$     | 0.30              |  |  |

| <sup>1</sup> throughput recale                                                   | culated for authenticate                                                             | ed encryption  | based on HM   | IAC-(hash fu | nction) and C' | TR-(block cipher) |  |  |

|                                                                                  | <sup>2</sup> this design offers Grøstl-256, Grøstl-512, AES-128, AES-192 and AES-256 |                |               |              |                |                   |  |  |

| <sup>3</sup> this design offers ECHO-256, ECHO-512, AES-128, AES-192 and AES-256 |                                                                                      |                |               |              |                |                   |  |  |

| <sup>4</sup> this design uses one extra block RAM                                |                                                                                      |                |               |              |                |                   |  |  |

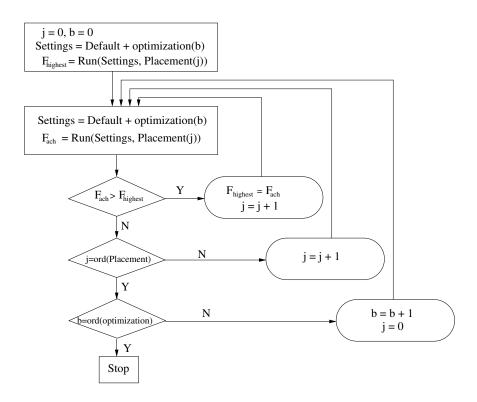

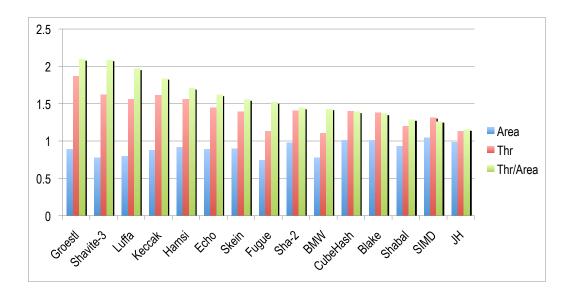

|                                                                                  | <sup>5</sup> this                                                                    | design uses to | wo extra bloc | k RAMs       |                |                   |  |  |